#### МИНОБРНАУКИ РОССИИ

ФГБОУ ВПО «Уральский государственный лесотехнический университет»

Кафедра автоматизации производственных процессов

Ордуянц Г.Г. Тойбич В.Я.

# Проектирование и исследование комбинационных схем в оболочке MultiSim

Методические указания к курсовой работе по Интегральной схемотехнике для специальностей 220301, 220200, 220400 и 220700 очной и заочной форм обучения

Печатается по рекомендации методической комиссии факультета ЛИФ УГЛТУ Протокол  $N_2$  от 2013г.

Рецензент кандидат технических наук, доцент С.П. Санников

### Редактор

| Подписано печать | Формат 60х84 1/16 |               |

|------------------|-------------------|---------------|

| Плоская печать   | Печ. л.           | Тираж 50 экз. |

| Поз.             | Заказ №           | Цена          |

Редакционно-издательский отдел УГЛТУ Отдел оперативной полиграфии УГЛТУ

#### Общие сведения

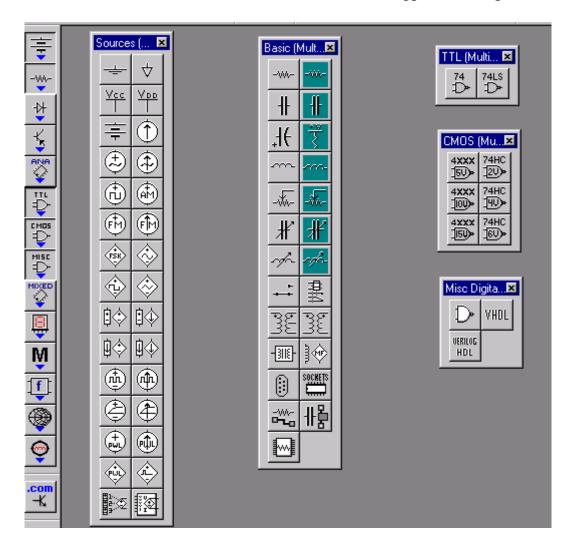

Из библиотеки компонентов и инструментов MulniSim в ходе создания и исследования комбинационных схем рекомендуется использовать следующие элементы и приборы:

1. Источники питания 2. Пассивные элементы 3. Цифровые микросхемы

4.Индикаторы

5. Электромеханические устройства

#### 6.Измерительные приборы и средства анализа:

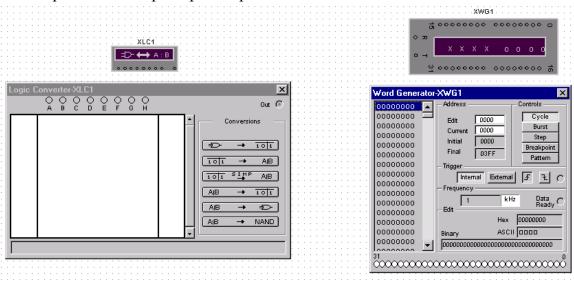

Логический преобразователь

Генератор слов

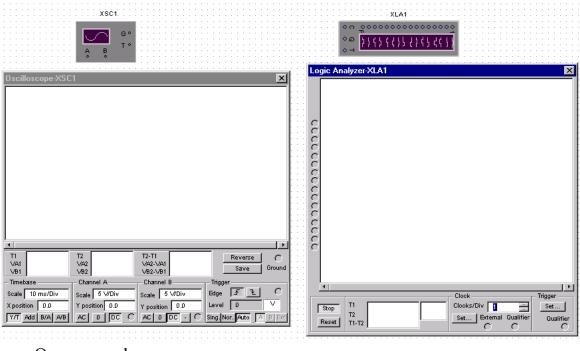

Осцилограф

Логический анализатор

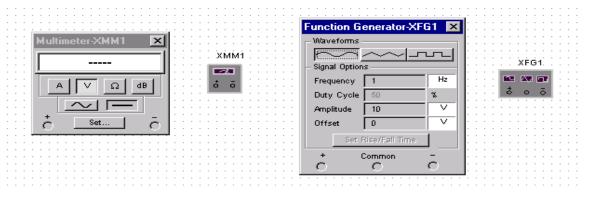

Мультиметр

Функциональный генератор

Для перенесения компонента из библиотеки на рабочее поле курсор мыши подводится к значку соответствующего раздела, при этом его название подсвечивается. После выбора компонента курсором мыши и нажатия ее левой кнопки (отмена выбора- нажатие правой кнопки) возможны два варианта. В первом, наиболее простом случае, курсор мыши в форме стрелки с выбранным компонентом переносится на рабочее поле и нажимается левая кнопка мыши. Во втором случае выбор компонента сопровождается вызовом окна. Если необходимо отредактировать параметры компонента, то в этом окне нажимается кнопка Edit, проводится коррекция параметров, и только после нажатия кнопки ОК в этом окне курсор мыши принимает указанную форму.

Для прокладки соединительных проводников курсор мыши необходимо подвести к выводу компонента и когда курсор примет крестообразную форму, нажать-отпустить левую кнопку мыши, проводник в виде пунктирной линии протянуть к выводу второго компонента и повторно нажать-отпустить левую кнопку. Для удаления проводника он выделяется и нажимается клавиша Delete. При изменении формы проводника он отмечается, при этом точки его перегибов и соединений с выводами компонента отмечаются квадратиками, которые и служат для перемещения курсором мыши его отдельных частей.

При установке курсора мыши на иконку прибора или на любой другой компонент схемы и нажатия ее правой кнопки, вызывается динамическое меню, позволяющее вырезать (Cut), копировать (Copy), изменить цвет (Color) компонента, а также выполнить четыре команды по его перемещению (вращению).

При необходимости удаления в буфер, копирования, изменения цвета или перемещения компонента целесообразно воспользоваться соответствующими командами из меню Edit. Если требуется размножить некоторый компонент, то после его копирования курсор мыши ставится на свободное место рабочего поля и нажатием правой кнопки мыши вызывается второе динамическое меню, отличающееся от первого большим числом команд. После выбора из этого меню команды вставки Paste курсор мыши с прицепившимся к нему значком компонента устанавливается в требуемое место будущей схемы и нажимается левая кнопка мыши. Если компонент необходимо вставить в разрыв проводника, то он устанавливается так, чтобы его выводы с обеих сторон совпали с проводником, после чего нажимается левая кнопка мыши. Для удаления компонента он отмечается и нажимается клавиша Delete, при этом удаляются и присоединенные к нему проводники.

#### Порядок проведения работы

- 1.Собрать на рабочем поле комбинационную схему соответственно полученному заданию.

- 2.Оснастить вход-выход контрольно-измерительными приборами. Для задания входных аргументов можно применить генератор слов или электромеханические переключатели, а выходные функции удобно контролировать при помощи индикаторных лампочек и семисегментных и линейных индикаторов.

- 3.Задавая генератором слов или переключателями последовательности входных слов, провести исследование схемы, заполнить таблицы истинности или вывести математическую модель логического устройства.

#### Пример

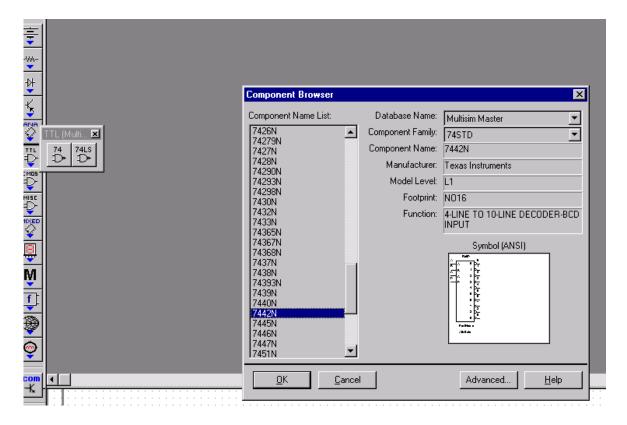

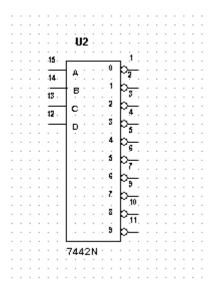

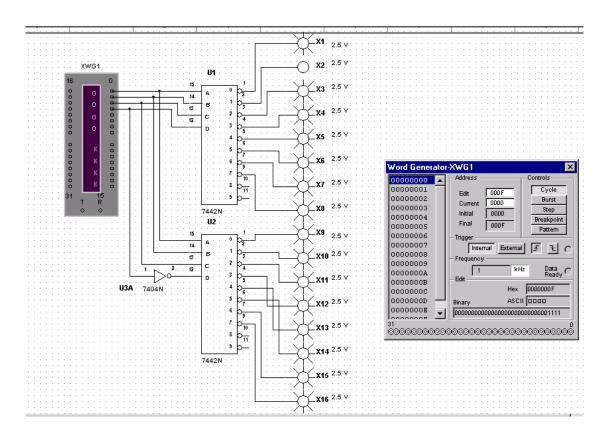

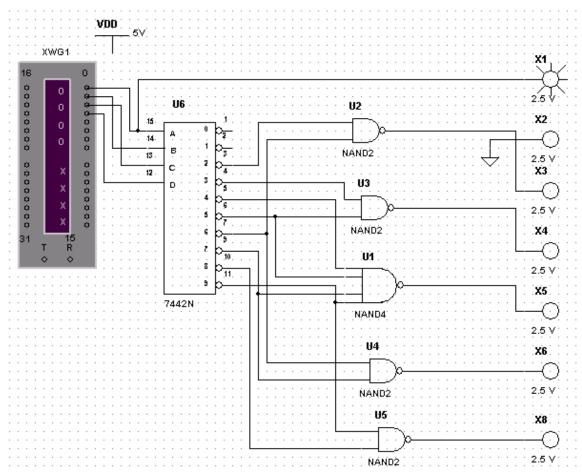

Задание: Провести исследование дешифратора двоичных сигналов на основе микросхемы серии ТТЛ – 7442N, составить схему наращивания.

Из библиотеки элементов ТТЛ выберем дешифратор 7442N.

После нажатия мышью клавиши ОК, выбранный дешифратор переместится на рабочее поле.

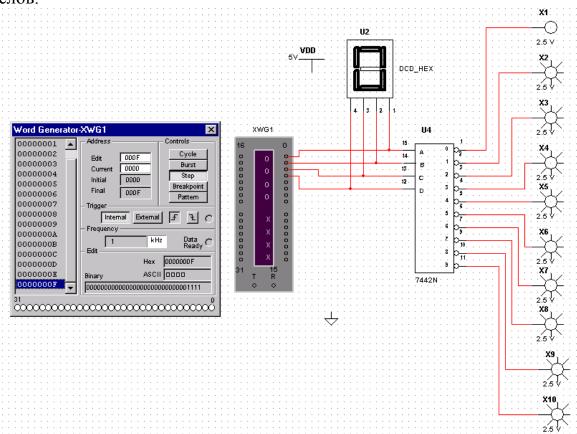

Оснастим схему средствами контроля и запрограммируем генератор слов.

Исследование схемы проведем в ручном режиме, поэтому при каждом нажатии курсором мыши на клавишу Step на панели генератора слов на входы дешифратора будут в пошаговом режиме поступать новые слова. Полученные данные занесем в табл.1.

Таблица 1 Состояния дешифратора 7442N

| BX | ВХОДЫ ВЫХОДЫ |   |   |   |   |   |   |   |   |   |   |   |   |

|----|--------------|---|---|---|---|---|---|---|---|---|---|---|---|

| D  | C            | В | A | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0  | 0            | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0  | 0            | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0  | 0            | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0  | 0            | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0  | 1            | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0  | 1            | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0  | 1            | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0  | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1  | 0            | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1  | 0            | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1  | 0            | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1  | 0            | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1  | 1            | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1  | 1            | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1  | 1            | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1  | 1            | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| _  |              |   |   |   |   |   |   |   |   |   |   |   |   |

|    |              |   |   |   |   |   |   |   |   |   |   |   |   |

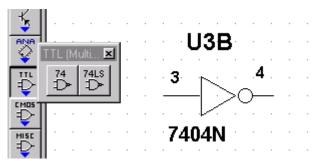

Вывод: Исследуемый дешифратор преобразует двоичный код поступающий на входы ABCD в сигнал низкого уровня, появляющийся на одном из десятичных выходов 0-9. Если десятичный эквивалент входного кода превышает 9, то на всех выходах 0-9 появляются напряжения высокого уровня. Если ограничить поступающий входной код от 0 до 8, то вход D можно использовать как разрешающий с низким активным уровнем, что дает возможность увеличить количество выходов до 16. Для инвертирования разряда D можно применить одну из секций микросхемы 7404N, которую также можно извлечь из библиотеки ТТЛ.

Соберем на рабочем поле схему наращивания, сигналы на входы подадим от генератора слов.

Результаты исследования занесем в табл. 2.

Таблица 2

Состояния дешифратора вида 4:16

| Вход |   |    |   |   |   |    | Выход |   |       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|------|---|----|---|---|---|----|-------|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|      | J | J2 |   |   | J | J1 |       |   | U1 U2 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| D    | C | В  | A | D | C | В  | A     | 0 | 1     | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 1    | 0 | 0  | 0 | 0 | 0 | 0  | 0     | 0 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 0 | 0  | 1 | 0 | 0 | 0  | 1     | 1 | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 0 | 1  | 0 | 0 | 0 | 1  | 0     | 1 | 1     | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 0 | 1  | 1 | 0 | 0 | 1  | 1     | 1 | 1     | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 1 | 0  | 0 | 0 | 1 | 0  | 0     | 1 | 1     | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 1 | 0  | 1 | 0 | 1 | 0  | 1     | 1 | 1     | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 1 | 1  | 0 | 0 | 1 | 1  | 0     | 1 | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1    | 1 | 1  | 1 | 0 | 1 | 1  | 1     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0    | 0 | 0  | 0 | 1 | 0 | 0  | 0     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0    | 0 | 0  | 1 | 1 | 0 | 0  | 1     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0    | 0 | 1  | 0 | 1 | 0 | 1  | 0     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0    | 0 | 1  | 1 | 1 | 0 | 1  | 1     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0    | 1 | 0  | 0 | 1 | 1 | 0  | 0     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0    | 1 | 0  | 1 | 1 | 1 | 0  | 1     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0    | 1 | 1  | 0 | 1 | 1 | 1  | 0     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0    | 1 | 1  | 1 | 1 | 1 | 1  | 1     | 1 | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

#### Варианты задания:

- 1.Спроектировать и исследовать схему преобразователя трехразрядного двоичного кода в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента.

- 2. Спроектировать и исследовать схему преобразователя четырехразрядного двоичного кода в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента. Смотри приложение.

- 3.Спроектировать и исследовать схему преобразователя четырехразрядного двоичного кода в сигналы управления двумя разрядами 7-ми сегментных индикаторов с выводами от каждого сегмента.

- 4.Спроектировать и исследовать схему для дешифрации четырех разрядного двоичного кода на дешифраторах вида 3:8.

- 5.Спроектировать и исследовать схему преобразователя трехразрядного кода Грея в сигналы управления одноразрядным 7-ми сегментным индикатором с выводами от каждого сегмента.

- 6. Спроектировать и исследовать схему преобразователя четырехразрядного кода Грея в сигналы управления двумя разрядами 7-ми сегментных индикаторов с выводами от каждого сегмента.

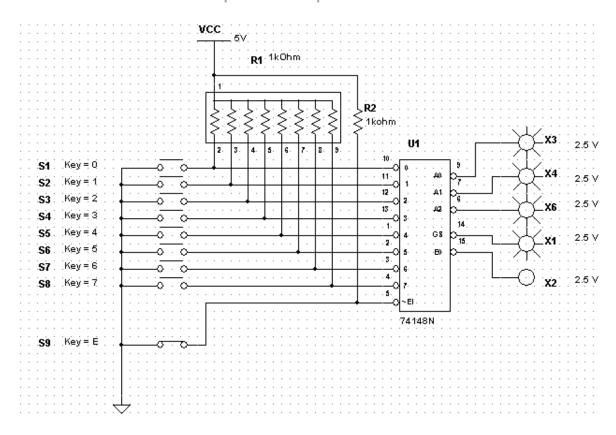

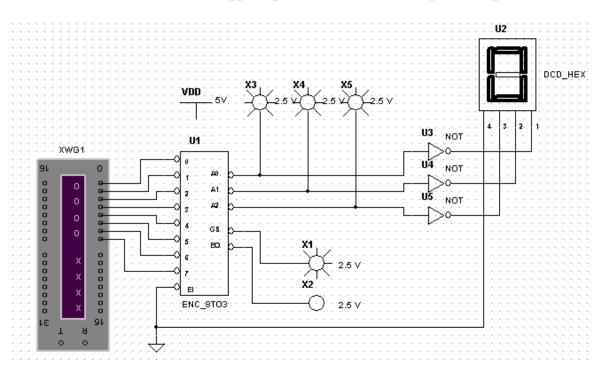

- 7. Провести исследование приоритетного шифратора вида 8:3. Смотри приложение.

- 8. Провести исследование приоритетного шифратора вида 10:4.

- 9.Спроектировать и исследовать схему шифратора вида 16:4 с использованием двух шифраторов вида 8:3.

- 10.Спроектировать и исследовать мультиплексор вида 4:1, построенный на логических элементах И, ИЛИ, НЕ.

- 11.Спроектировать и исследовать схему мультиплексора вида 16:1 с использованием двух мультиплексоров вида 8:1.

- 12.Спроектировать и исследовать схему мультиплексора вида 16:1 из мультиплексоров вида 4:1.

- 13.Синтезировать и исследовать схему полусумматора двух одноразрядных двоичных чисел на логических элементах И-НЕ.

- 14.Синтезировать и исследовать схему полного одноразрядного сумматора на элементах 2И-ИЛИ-НЕ.

- 15. Спроектировать и исследовать схему четырехразрядного инкрементора на HALF ADDER (полусумматор) из библиотеки MISC.

- 16.Спроектировать и исследовать схему сумматора для сложения двух четырехразрядных двоичных чисел на HALF ADDER (полусумматор) из библиотеки MISC.

- 17.Спроектировать и исследовать схему сумматора-вычитателя двух четырехразрядных двоичных чисел.

- 18.Спроектировать и исследовать схему устройства для сравнения двух четырехразрядных двоичных чисел на основе четырехразрядного сумматора-вычитателя.

- 19.Спроектировать и исследовать схему устройства для вычисления среднего арифметического двух четырехразрядных двоичных чисел.

- 20.Спроектировать и исследовать схему для сложения четырехразрядного двоичного числа с пятиразрядной двоичной константой.

- 21.Спроектировать и исследовать схему для возведения в квадрат трехзначного двоичного числа. Смотри приложение.

- 22. Спроектировать и исследовать схему для перемножения двухразрядных двоичных чисел.

- 23. Спроектировать и исследовать схему для перемножения двухразрядного и трехразрядного двоичного числа.

- 24.Спроектировать и исследовать схему преобразователя кодов согласно нижеприведенной таблице.

Указание: схему выделения старшей единицы реализовать:

- а) на шифраторе и дешифраторе вида 8:3;

- в) на элементах М2. Смотри приложение;

- с) на элементах И-НЕ.

| Входной код |   |   |   |   |   |   |   | Показания индикатора по последней цифре номера зачетной |        |   |   |   |   |   |   |   |   |  |  |  |

|-------------|---|---|---|---|---|---|---|---------------------------------------------------------|--------|---|---|---|---|---|---|---|---|--|--|--|

|             |   |   |   |   |   |   |   |                                                         | книжки |   |   |   |   |   |   |   |   |  |  |  |

|             |   |   |   |   |   |   |   | 0                                                       | 1      | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |  |  |  |

| 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0                                                       | 1      | L | 8 | Π | 0 | Н | 2 | Е | 0 |  |  |  |

| 0           | 0 | 0 | 0 | 0 | 0 | 0 | 1 | A                                                       | 2      | 0 | Γ | 3 | 8 | P | 0 | 6 | 8 |  |  |  |

| 0           | 0 | 0 | 0 | 0 | 0 | 1 | 1 | b                                                       | 3      | F | 9 | 0 | 6 | О | 1 | L | A |  |  |  |

| 0           | 0 | 0 | 0 | 0 | 1 | 1 | 1 | С                                                       | 4      | 1 | С | 4 | 4 | П | 8 | 9 | С |  |  |  |

| 0           | 0 | 0 | 0 | 1 | 1 | 1 | 1 | d                                                       | 5      | d | 5 | С | 2 | Ь | 7 | A | L |  |  |  |

| 0           | 0 | 0 | 1 | 1 | 1 | 1 | 1 | Е                                                       | 6      | 2 | S | A | 4 | Γ | 3 | 2 | 3 |  |  |  |

| 0           | 0 | 1 | 1 | 1 | 1 | 1 | 1 | F                                                       | 7      | P | 9 | 6 | 6 | Е | 4 | Н | 7 |  |  |  |

| 0           | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Н                                                       | 8      | 3 | Е | P | 8 | Ч | 6 | 5 | 1 |  |  |  |

| 1           | 1 | 1 | 1 | 1 | 1 | 1 | 1 | P                                                       | 9      | С | 1 | 7 | 0 | Ц | 5 | d | F |  |  |  |

25. Спроектировать и исследовать схему преобразователя трехразрядных двоичных кодов на мультиплексорах вида 8:1, согласно нижеприведенной таблице.

| В | XO | Д | ВЫХОД |   |   |  |  |  |  |

|---|----|---|-------|---|---|--|--|--|--|

| С | В  | A | Z     | Y | X |  |  |  |  |

| 0 | 0  | 0 | 1     | 0 | 0 |  |  |  |  |

| 0 | 0  | 1 | 0     | 1 | 0 |  |  |  |  |

| 0 | 1  | 0 | 0     | 0 | 1 |  |  |  |  |

| 0 | 1  | 1 | 0     | 1 | 0 |  |  |  |  |

| 1 | 0  | 0 | 1     | 0 | 0 |  |  |  |  |

| 1 | 0  | 1 | 0     | 1 | 0 |  |  |  |  |

| 1 | 1  | 0 | 0     | 0 | 1 |  |  |  |  |

| 1 | 1  | 1 | 0     | 1 | 0 |  |  |  |  |

#### ПРИЛОЖЕНИЕ

В приложении приводятся схемы реализации некоторых вариантов заданий. Следует помнить, что приведенные схемы не претендуют на роль «истины в последней инстанции», а только демонстрируют возможности программы Multisim. Например, исследование шифратора вида 8:3 можно проводить в режиме ручного управления при помощи кнопок (схема 2), а можно автоматизировать этот процесс при помощи программируемого генератора слов, как это сделано в схеме 3.

#### СХЕМЫ

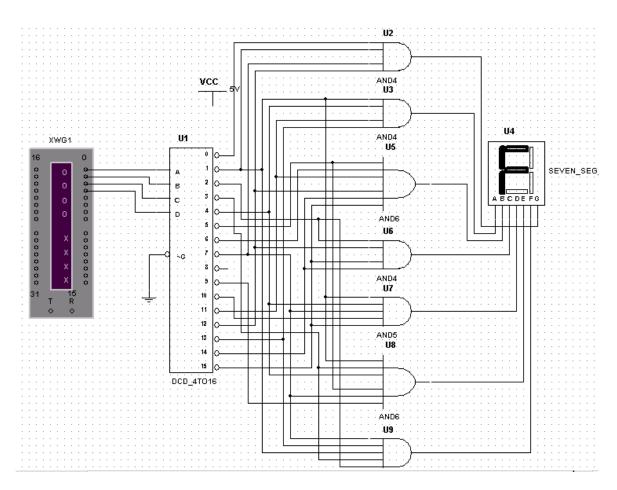

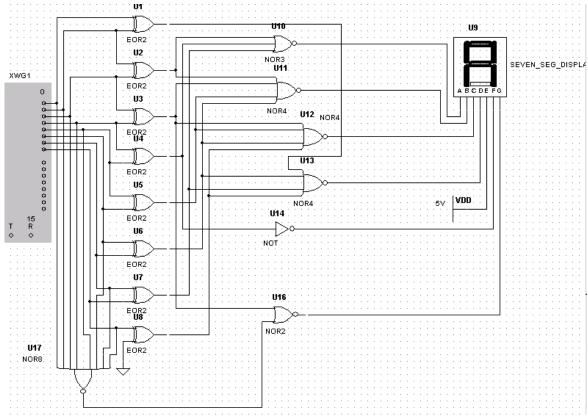

Схема 1. Дешифратор управления сегментами индикатора

В схеме применен некий гипотетический дешифратор имеющий инверсные выходы из библиотеки MISC. Если принцип образования схемы понятен, попытайтесь самостоятельно сконструировать аналогичный преобразователь с использованием дешифратора с прямыми выходами, например 4028 из библиотеки CMOS (КМОП).

Схема 2. Исследование шифратора 74148 вида 8:3 в ручном режиме.

Схема 3. Исследование шифратора вида 8:3 при помощи генератора слов.

Схема 4. Устройство для возведения в квадрат двоичных чисел.

Схема 5. Преобразователь унитарного кода в семисегментный с узлом выделения старшей единицы на элементах M2.